BMS 典型应用- I2C 应用指导手册

V1.0

## 摘要

本文档对 BMS 应用的 I2C 功能模块进行详细介绍,方便用户快速进行 I2C 相关功能开发。在生产和使用过程中,可能会遇到电量计通讯异常的问题。电量计通讯异常是一个非常宽泛的问题,存在各种各样的原因可以导致电量计通讯异常。汇总起来,可以分成两大类:硬件(HW)导致的通讯异常和固件(FW)导致的通讯异常。本章详细介绍了一些通用的处理电量计通讯异常的方法,并提供一些实际解决电量计通讯异常的案例,以供参考。

## 版本

| 历史版本 | 修改内容 | 日期         |

|------|------|------------|

| V1.0 | 初版生成 | 2022-09-10 |

# 目录

| 1 典型应用框图           | 3  |

|--------------------|----|

| 2 I2C 协议介绍         |    |

| 2.1 物理拓扑结构         | 4  |

| 2.2 总线特征           | 4  |

| 2.3 总线协议           | 4  |

| 2.4 I2C 底层通信流程梳理   | 6  |

| 2.4.1 发送流程         |    |

| 2.4.2 接收流程         | 8  |

| 3 应用约束             | 10 |

| 3.1 正常模式           | 10 |

| 3.2 异常时序           | 10 |

| 3.2.1 总线空闲电平不为高    |    |

| 3.2.2 Start 信号异常   |    |

| 3.2.3 一主多从         | 12 |

| 3.2.4 I2C 硬件异常     | 12 |

| 4 I2C 硬件设计指导       | 13 |

| 4.1 上拉电阻的选取        |    |

| 4.2 限流电阻           |    |

| 4.2.1 限流电阻的取值      |    |

| 4.2.2 限流电阻不符合要求的影响 | 14 |

| 4.3 保护二极管          | 15 |

| 4.4 布局建议           | 15 |

| 4.4.1 硬件约束建议       |    |

| 4.4.2 未进行约束处理的影响   |    |

| 5 单节电量计通讯异常的分析方法   | 17 |

| 5.1 硬件异常导致不能通讯     |    |

| 5.2 FW 异常导致不能通讯    | 18 |

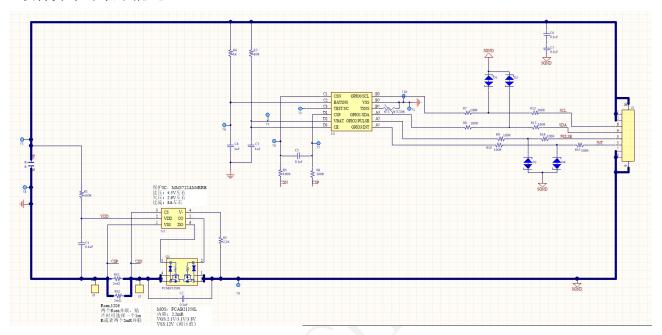

## 1 典型应用框图

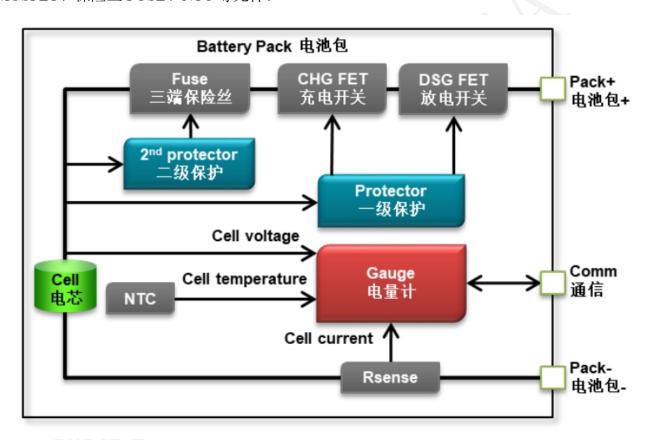

对于电池供电的产品,比如手机、笔记本电脑、电动车等,我们都希望知道其电池还剩多少电、还能用多久,以便我们能放心使用,避免使用过程中电量用光而宕机。这就需要电量计告诉我们这些信息。

如下图所示,一个典型的电池包框架,电池包内部包含电芯,电量计 IC,保护 IC,充放电 MOSFET、保险丝 FUSE、NTC 等元件。

图 1 典型电量计应用框图

## 2 I2C 协议介绍

I2C 是 Inter-Integrated Circuit 的简称,读作: I-squared-C。由飞利浦公司于 1980 年代提出,为了让主板、嵌入式系统或手机用以连接低速周边外部设备而发展。主要用于 SOC 和周边外设间的通信。

#### 2.1 物理拓扑结构

I2C 总线在物理连接上非常简单,分别由 SDA(串行数据线)和 SCL(串行时钟线)及上 拉电阻组成。通信原理是通过对 SCL 和 SDA 线高低电平时序的控制,来产生 I2C 总线协议 所需要的信号进行数据的传递。在总线空闲状态时,这两根线一般被上面所接的上拉电阻拉高,保持着高电平。

### 2.2 总线特征

I2C 总线上的每一个设备都可以作为主设备或者从设备,而且每一个设备都会对应一个唯一的地址(地址通过物理接地或者拉高,可以从 I2C 器件的数据手册得知,BMS 的芯片默认 7 位地址,7 位地址依次 bit6~bit0,地址范围为 0x00~0x7F,而之所以 7bit 因为 1 个 bit 要代表方向,主向从和从向主),主从设备之间就通过这个地址来确定与哪个器件进行通信,在通常的应用中,我们把 CPU 带 I2C 总线接口的模块作为主设备,把挂接在总线上的其他设备都作为从设备。

I2C 总线上可挂接的设备数量受总线的最大电容限制,如果所挂接的是相同型号的器件,则还受器件地址位的限制。

I2C 总线数据传输速率在标准模式下可达 100kbit/s, 快速模式下可达 400kbit/s, 高速模式下可达 3.4Mbit/s。一般通过 I2C 总线接口可编程时钟来实现传输速率的调整, 同时也跟所接的上拉电阻的阻值有关。

I2C 总线上的主设备与从设备之间以字节(8位)为单位进行双向的数据传输。

#### 2.3 总线协议

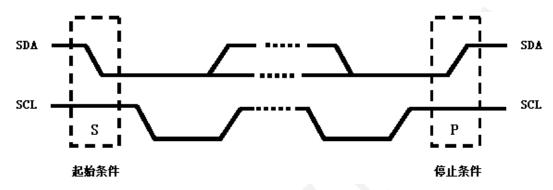

I2C 协议规定,总线上数据的传输必须以一个起始信号作为开始条件,以一个结束信号作为传输的停止条件。起始和结束信号总是由主设备产生(意味着从设备不可以主动通信?所有的通信都是主设备发起的,主可以发出询问的 command,然后等待从设备的通信)。

起始和结束信号产生条件:总线在空闲状态时,SCL和SDA都保持着高电平,当SCL为高电平而SDA由高到低的跳变,表示产生一个起始条件;当SCL为高而SDA由低到高的跳变,表示产生一个停止条件。

在起始条件产生后,总线处于忙状态,由本次数据传输的主从设备独占,其他 I2C 器件 无法访问总线;而在停止条件产生后,本次数据传输的主从设备将释放总线,总线再次处于 空闲状态。起始和结束如图所示:

图 2 I2C 起始和结束波形

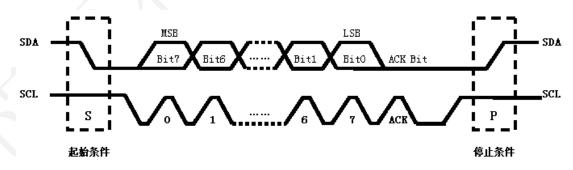

在了解起始条件和停止条件后,我们再来看看在这个过程中数据的传输是如何进行的。 前面我们已经提到过,数据传输以字节为单位。主设备在 SCL 线上产生每个时钟脉冲的过程中将在 SDA 线上传输一个数据位,当一个字节按数据位从高位到低位的顺序传输完后, 紧接着从设备将拉低 SDA 线,回传给主设备一个应答位,此时才认为一个字节真正的被传输完成。当然,并不是所有的字节传输都必须有一个应答位,比如:当从设备不能再接收主设备发送的数据时,从设备将回传一个否定应答位。数据传输的过程如图所示:

图 3 I2C 数据传输过程

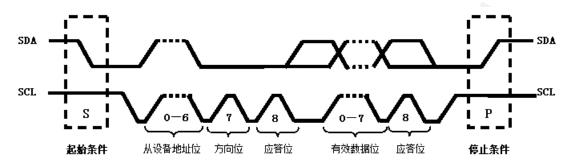

在前面我们还提到过,I2C 总线上的每一个设备都对应一个唯一的地址,主从设备之间的数据传输是建立在地址的基础上,也就是说,主设备在传输有效数据之前要先指定从设备的地址,地址指定的过程和上面数据传输的过程一样,只不过大多数从设备的地址是7位的,然后协议规定再给地址添加一个最低位用来表示接下来数据传输的方向,0表示主设备向从设备写数据,1表示主设备向从设备读数据。向指定设备发送数据的格式如图所示: (每一最小包数据由9bit组成,8bit内容+1bit ACK,如果是地址数据,则8bit包含1bit方向)。

图 4 I2C 数据传输波形格式

## 2.4 I2C 底层通信流程梳理

#### 2.4.1 发送流程

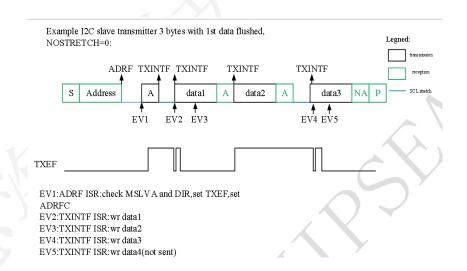

图 5 I2C 数据发送流程图 (NOSTRETCH = 0))

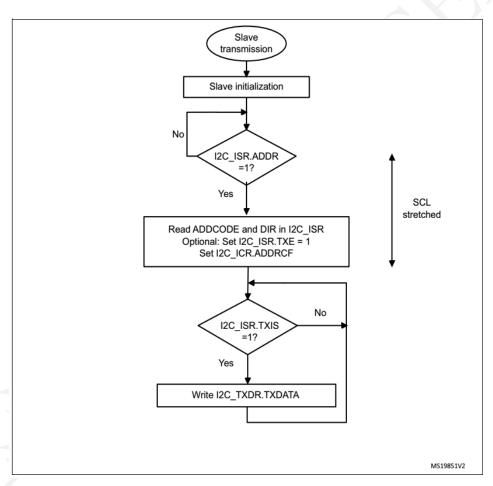

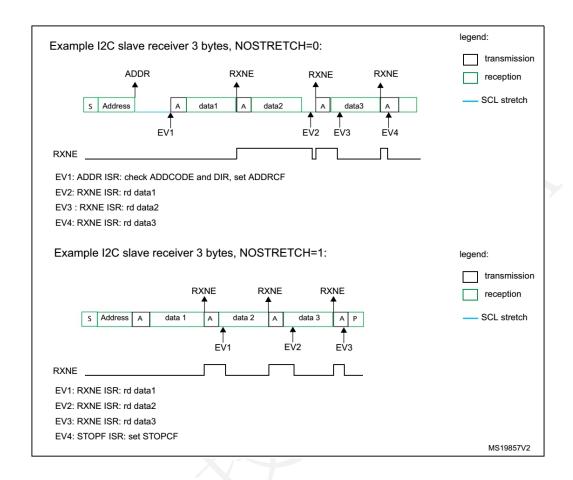

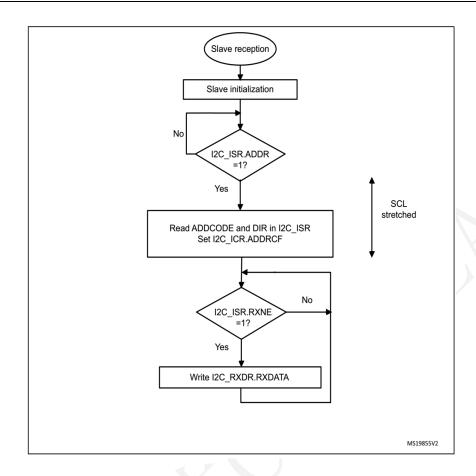

## 2.4.2 接收流程

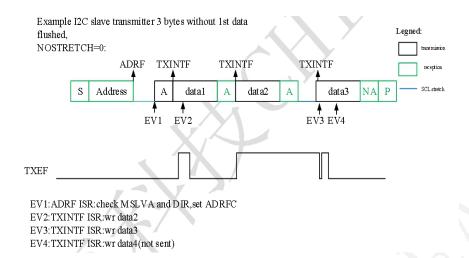

图 6 I2C 数据接受流程图 (NOSTRETCH = 0))

## 3 应用约束

## 3.1 正常模式

在正常模式下,BMS 的芯片设计依据标准的 I2C 协议规范,在主机系统遵循相关的时序规范条件下,均能正常进行通信,无条件约束。

## 3.2 异常时序

### 3.2.1 总线空闲电平不为高

#### 3.2.1.1 总线异常时序

若总线电平在空闲状态不为高,则会导致其从睡眠唤醒,到正常通信,第一笔通信数据会出现 NACK,后续通信恢复正常。

#### 3.2.1.2 深度睡眠机制说明

I2C 能够在被寻址到的时候将 MCU 从 DEEPSLEEP1、2 模式唤醒(APB 时钟关闭时),支持所有的地址模式。进入深度睡眠前,SDA 和 SCL 需要 HFO 上一次关闭前,采样的 SDA 电平状态为 1 或者 SCL 的电平状态为 1,再次睡眠唤醒则能正常的识别到 start 信号。

将 I2Cx CR1 寄存器的 WUPEN 位置 1,会启用从 DEEPSLEEP1、2 模式唤醒功能。

在 DEEPSLEEP1、2 模式下,HFO 是关闭的。当检测到起始条件,I2C 接口将启动 HFO,然后将 SCL 拉低,直到 HFO 启动完毕。HFO 随后用于地址接收,在地址匹配的情况下,在 MCU 唤醒期间 I2C 将 SCL 持续拉低。当软件清除了 ADDR 标志后,SCL 被释放,传输进入正常状态。

如果地址不匹配,HFO会再次关闭,MCU也不会被唤醒。

注:

- ① 如果 I2C 时钟是系统时钟,或者如果 WUPEN = 0,HFO 振荡器在收到 START 后不会被打开。

- ② 只有 ADDR 中断可以唤醒 MCU。所以,在 I2C 作为主机正在传输数据的时候,或者作为从机在被寻址到(ADDR=1)的时候,不要进入 DEEPSLEEP1、2 模式。这可以用在 ADDR 中断服务程序中清除 SLEEPDEEP 位,并只在 STOPF 标志置 1 后重新将它置 1 的方式来管理。

- ③ 数字滤波器和从 DEEPSLEEP1、2 模式唤醒功能不兼容。如果 DNF 位不等于 0,设置 WUPEN 位会没有任何效果。

- ④ 只有当 I2C 的时钟源是 HFO 振荡器的时候此功能可用。

- ⑤ 必须启用时钟延长功能(NOSTRETCH=0),以确保正常从停止功能唤醒。

地址匹配: 从睡眠正常唤醒的条件: 进入深度睡眠前,总线电平,SCL和 SDA 需要空闲为高唤醒的从机,地址匹配的时候,在主机发送地址匹配时,则主频高速时钟在 2us 左右起振。后续正常通信期间,高频时钟一直建立。

若地址不匹配,在 30 个时钟周期后,从机关闭高频时钟 HFO,系统处理完任务后再次进入深度睡眠。

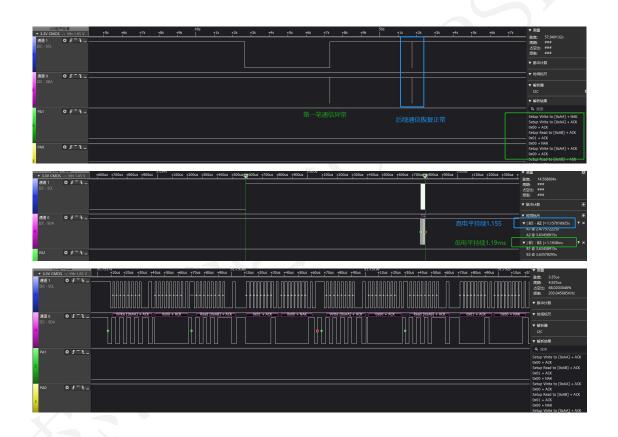

#### 3.2.2 Start 信号异常

当 SDA 和 SCL 同时由高变低,或者当 SCL 为低电平时,SDA 出现下降沿,此时会触发 I2C 的复位机制,若复位期间(20us 左右),出现了 I2C 通信,则会出现第一笔通信数据 NACK,后续通信恢复正常,

SDA 和 SCL 同时由高变低时序图

当 SCL 为低电平时,SDA 出现下降沿的时序图(下列的低电平时间只是一个示例,持续的时间在主循环执行周期内,若应用的主循环执行周期是 200uS,则 200uS 以内,均可能触发第一笔通信的异常)

#### 3.2.3 一主多从

在一主多从的应用系统中,其他从机的单笔通信连续超过 100ms,则会触发电量计的应用层的 I2C 超时复位。对其他从机通信无影响。

应用代码中, I2C 的超时复位, 仅复位 I2C 外设模块, 电量计切勿对 I2C 的 GPIO 进行初始化, 否则会在初始化期间, 拉低总线时钟, 可能影响其他从机的通信传输。

#### 3.2.4 I2C 硬件异常

在总线上无上拉电阻的时候,因为总线处于浮空状态,此时若时序上正好构建了一个 start 信号,则会唤醒电量计。

电量计唤醒, 若地址不匹配在 30 个时钟周期后, 大约 4uS 左右, 系统高频时钟会关闭, 待主机完成主循环任务, 则会立即进入休眠状态。

例如在电池运输状态, pack 包未组装到主机端,此时 I2C 总线处于浮空状态,会存在被唤醒的可能,但其处于正常模式的时间很短,大约在 4uS 左右,其芯片平均功耗非常小,接近深度睡眠的 20uA 以内功耗。

www.chipsea.com

12 / 19

芯海科技(深圳)股份有限公司

## 4 I2C 硬件设计指导

#### 4.1 上拉电阻的选取

上拉电阻设置满足 I2C 协议要求(电源电压限制了上拉电阻的最小值; 负载电容(总线电容)限制了上拉电阻的最大值)。如果上拉电阻过大,加上线上的总线电容,由于 RC 影响,会带来上升时间的增大(下降延是芯片内的晶体管,是有源驱动,速度较快;上升延是无源的外接电阻,速度慢),而且上拉电阻过大,即引起输出阻抗的增大,当输出阻抗和负载的阻抗可以比拟的时,则输出的高电平会分压而减少。

电阻的大小对时序有一定影响,对信号的上升时间和下降时间也有影响,一般接 1.5K 或 2.2K。

空闲状态下,两条信号线应该维持高电平。否则,上拉电阻上会有漏电。

#### 4.2 限流电阻

#### 4.2.1 限流电阻的取值

I2C 协议定义了串联在 SDA、SCL 线上电阻 Rs。该电阻的作用是,有效抑制总线上的干扰脉冲进入从设备,提高可靠性。这个电阻的选择一般在 100ohm 左右(理论推导小于 257  $\Omega$ ,因芯片制造,存在个体差异,建议限流电阻小于  $200\,\Omega$ )。当然,这个电阻并不是必须的,在恶劣噪声环境中,可以选用,同时起到限流作用。

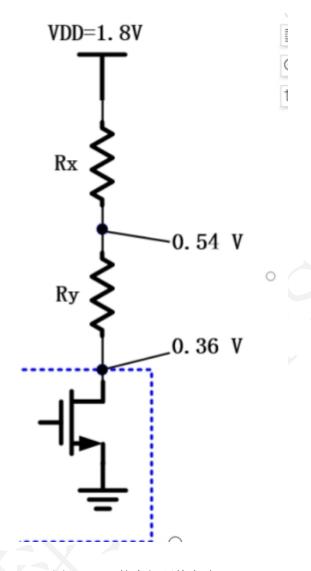

图中标 0.36V 处为 BMS 的的 I2C 输出引脚, Ry 为限流电阻, Rx 为上拉电阻, 标 0.54V 处为板级 I2C 与其它芯片连接处。根据 VIL 指标,通信电压<=0.54V 就可以被识别为低电平, 不会出现通信电平错误。根据 VOL 指标, BMS 的的 I2C 输出引脚电压可以保证<=0.36V。

如果可以满足引脚电压=0.36V时通信电压为 0.54V,则引脚电压<=0.36V时,通信电压一定<=0.54V

根据 Rx 与 Ry 的电流相等,可以得到等式。由于 Rx=1800Ohm,

可以得到限流电阻 Ry<=257Ohm

| PARAMETER        |                             | TEST CONDITIONS                                    | MIN  | TYP | MAX  | UNIT |

|------------------|-----------------------------|----------------------------------------------------|------|-----|------|------|

| V <sub>IH</sub>  | High-level input voltage    | SCL, SDA/HDQ, V <sub>REG18</sub> = 1.8 V           | 1.26 |     |      | V    |

| V <sub>IL</sub>  | Low-level input voltage low | V <sub>REG18</sub> = 1.8 V                         |      |     | 0.54 | V    |

| V <sub>OL</sub>  | Low-level output voltage    | I <sub>OL</sub> = 1 mA, V <sub>REG18</sub> = 1.8 V |      |     | 0.36 | V    |

| Cı               | Input capacitance           |                                                    |      |     | 10   | pF   |

| I <sub>lkg</sub> | Input leakage current       |                                                    |      | 1   |      | μA   |

图 7 I2C 的 GPIO 特性

图 8 I2C 的内部硬件电路

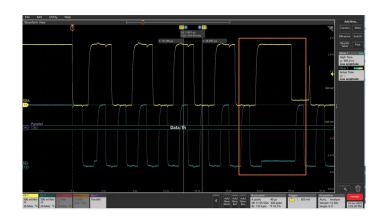

### 4.2.2 限流电阻不符合要求的影响

I2C漏极开路,当输出配置为低,输出驱动管下拉,输出驱动管有下拉电阻 Rmos, I2C 板级应用有限流电阻 Ry, I2C 等效下拉电阻 Rpull-down=Rmos+Ry, I2C 外部上拉电 Rpull-up。

当 I2C 时钟延展功能打开,I2C 漏极开路输出为低,实际电平为 I2C 漏极开路 Rpull-up、Rpull-down 分压,因此,会输出非零的低电平。当主机释放总线,从机开漏拉低,则会出现下图框图所示的波形。(如上图所示,上拉电阻为 Rx,限流电阻为 Ry)

根据上述的分析,当限流电阻小于  $257\,\Omega$ ,则半高电平不会影响通信,当限流电阻大于  $257\,\Omega$  的情形,则会影响 I2C 电平的判断。从而影响 I2C 通信。

#### 4.3 保护二极管

I2C上可以接上瞬态抑制二极管,比如 PESD5V0S1BL,保护器件,防止在 ESD 测试损坏 I2C 通讯时起到滤波作用。

#### 4.4 布局建议

#### 4.4.1 硬件约束建议

PCB 布局地线应尽量的粗。细的线电阻较大,电阻大的话会造成接地电位随着电流的变化而变化,这样的话会导致信号电平不稳,继而造成电路的抗干扰能力下降。

当电路板上信号频率高于 10MHz 时,由于布线的电感效应明显,地线阻抗变得很大,应采用多点接地,尽量降低地线阻抗。

走线应尽可能地减少过孔的数量,在 SDA 和 SCL 走线周围用 GND 包围。

上拉电阻应安置在 OD 输出端附近。当 I2C 总线上主从器件(Master & Slave)两端均为 OD 输出时,电阻放置在信号路径的中间位置。当主设备端是软件模拟时序,而从设备是 OD 输出时,应将电阻安置在靠近从设备的位置。

折叠、滑盖机型中,I2C的两根信号线需要通过转轴或滑轨处的FPC,此时由于信号路径比较长,距离天线比较近,而且 Open drain 的输出级对地阻抗大,对干扰比较敏感,因此比较容易受到 RF 信号源的干扰。在这种情况下,就应适当注意对 I2C 信号线的保护。比如 I2C 两条信号线(SDA,SCL)等长度地平行走线,两边加地线进行保护,避免临近层出现高速信号线等

#### 4.4.2 未进行约束处理的影响

若上述的特殊场景,对信号走线和布局有要求,未进行处理,则通信的可靠性会受到干扰,导致无法进行可靠的 I2C 通信。

## 5 单节电量计通讯异常的分析方法

#### 5.1 硬件异常导致不能通讯

图 9 单节电量计典型硬件电路

硬件(HW)导致的通讯异常又可以分为电量计芯片外围电路导致的通讯异常和电量计芯片本身导致的通讯异常等。当遇到电量计通讯异常的时候,我们首先需要排查的是硬件上的原因。可以按照下面的步骤来逐一排查:

BMS 的单节电量计,受限确保 CE 引脚处于高电平状态,一般和 VBAT 接在一起。

排查 SDA 和 SCL 通路上的硬件是否存在问题

例如限流电阻是否损坏,表现的症状是开路或者阻抗异常变大等

I2C 的对地保护二极管是否因 ESD 损坏,表现的症状是二极管对地短路后者阻抗异常等焊接问题导致的异常

根据如上的分析,在电池包没有与主机连接时,可以用万用表测量对应的阻抗判断硬件是否异常

测量 SDA\_CON、SCL\_CON(参考原理图中靠近 J1 端子) 端分别对地的阻抗。根据经验,正常值应该是几百 k,甚至上兆欧。如果与良品对比阻抗偏小,那可能是 D1,或 D2,或芯片 SCL 管 脚,或 SDA 管脚有硬件损坏。

测量 SDA\_CON 与 SCL\_CON 之间的阻抗。如果与良品对比阻抗偏小,那可能是 SDA 和 SCL 通路之间存在短路或漏电的情况。

测量 SDA\_CON 与 SCL\_CON 管脚之间的阻抗,SCL\_CON 与 SCL 管脚之间的阻抗。以上图为例,如果阻抗明显比 200 欧大,那可能是电阻虚焊,或者电阻被损坏。这里有一点建议,万用表的表笔需要点在芯片的管脚上,而不是 PCB 板的焊盘上。笔者曾经遇到过芯片的管脚和 PCB 板的焊盘之间存在虚焊或者裂缝的情况。如果万用表的表笔是点在 PCB 板的焊盘上,则会漏掉这种硬件异常,从而把分析问题带到错误的方向。

测量 SCL 和 SDA 的二极管特性是否正常。

- 1、对电源二极管:万用表调到二极管测试档位,红表笔接 GPIO,黑表笔接 B+,记录万用表显示电压(正常芯片是 1.24V 左右)。

- 2、对地二极管:万用表调到二极管测试档位红表笔接 B-,黑表笔接 GPIO,记录万用表显示电压(正常是 0.576V 左右)。

- 3、电源的二极管特性: 红表笔接 B-, 黑表笔接 B+正常电压是 0.51V。

## 5.2 FW 异常导致不能通讯

I2C 的初始化符合上述 2.3 章节的时序要求,从机地址,通信速率,时钟延展等需要正确的配置。

例如 I2C 的速率配置异常,当主机配置 100K,从机配置 400K 的情况,则会出现数据通信异常的情况,电量计无法正确的响应。

或者是时钟延展未打开的情况,当从机来不及响应 I2C 主机的通信请求,需要主机等待,则会把 SCL 拉低(Clock Stretch,时钟延展),直到电量计处理完,再释放 SCL 信号,继续进行通讯。此时若无延展,则主机会偶尔记录到 NACK 的现象。

# 芯海科技 CHIPSEA

股票代码:688595

### 免责声明和版权公告

本文档中的信息,包括供参考的 URL 地址,如有变更,恕不另行通知。

本文档可能引用了第三方的信息,所有引用的信息均为"按现状"提供,芯海科技不对信息的准确性、真实性做任何保证。

芯海科技不对本文档的内容做任何保证,包括内容的适销性、是否适用于特定用途,也不提供任何其他芯海科技提案、规格书或样品在他处提到的任何保证。

芯海科技不对本文档是否侵犯第三方权利做任何保证,也不对使用本文档内信息导致的任何侵犯知识产权的行为负责。本文档在此未以禁止反言或其他方式授予任何知识产权许可,不管是明示许可还是暗示许可。

Wi-Fi 联盟成员标志归 Wi-Fi 联盟所有。蓝牙标志是 Bluetooth SIG 的注册商标。

文档中提到的所有商标名称、商标和注册商标均属其各自所有者的财产,特此声明。

版权归 © 2022 芯海科技 (深圳) 股份有限公司, 保留所有权利。

www.chipsea.com

19 / 19

芯海科技(深圳)股份有限公司

本资料为芯海科技专有财产,非经许可,不得复制、翻印或转变其他形式使用。